No. AN9329 September 1993

# **Application Note**

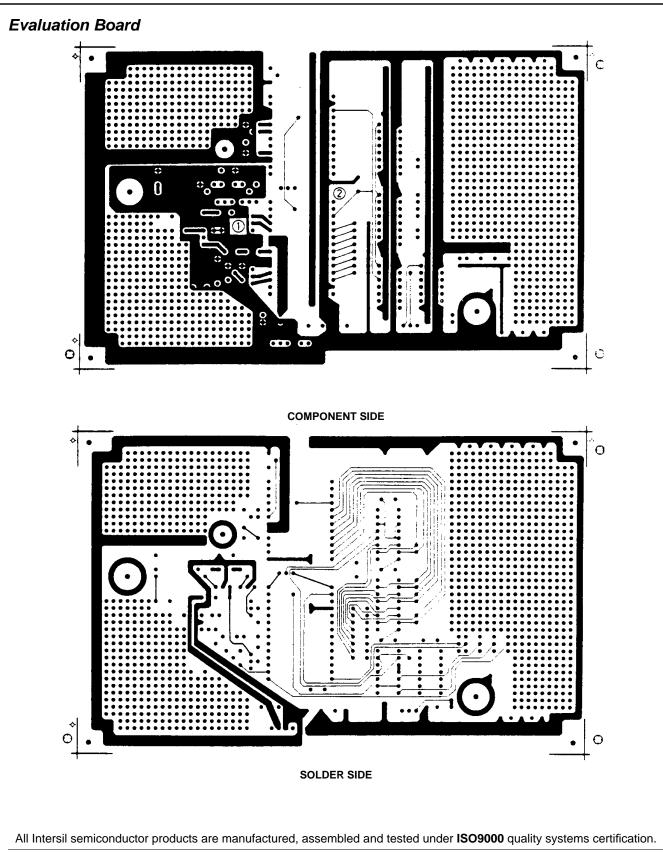

# Using the HI1176/HI1171 Evaluation Board

## Introduction

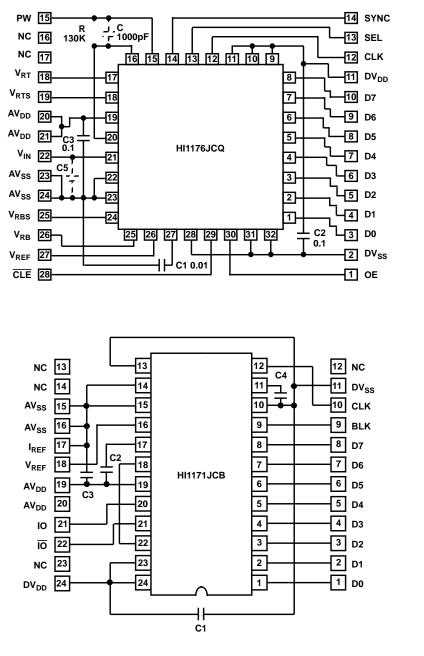

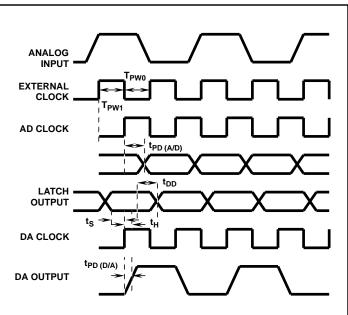

The HI1176 (8-bit, 20MSPS, ADC) and the HI1171 (8-bit, 40MHz, DAC) evaluation board is composed of a main board common to either type, to which is added a sub board specific to each part. Each sub board is connected to the main board through a socket. The main board has an input interface, a clock buffer, and a latch.

Each of the sub boards is mounted with an HI1176 and HI1171 respectively.

## Features

- 8-Bit Resolution

- 20MHz Conversion Rate

- CMOS Digital Input Level

### TABLE 1. SUPPLY VOLTAGE

| ITEM | MIN | ТҮР | МАХ | UNIT |

|------|-----|-----|-----|------|

| +5V  | -   | -   | 150 | mA   |

| -5V  | -   | -   | 20  | mA   |

#### TABLE 2. ANALOG OUTPUT (HI1171)

| ITEM          | MIN | ТҮР | МАХ | UNIT |  |

|---------------|-----|-----|-----|------|--|

| Analog Output | 0.5 | 2.0 | 2.1 | V    |  |

#### Functional Block Diagram VOUT ANALOG 8 DAC PROTOTYPE AREA LATCH DIGITAL PROTOTYPE AREA DATA VREF 8 ADC SOCKET ANALOG INPUT VIN INTERFACE CLOCK BUFFER osc ANALOG PROTOTYPE AREA sw GND CLOCK OE SEL SYNC CLE BLK THE HI1176JCQ AND HI1171JCB ADC/DAC EVALUATION BOARD

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures. 1-888-INTERSIL or 321-724-7143 | Copyright © Intersil Corporation 1999

| TABLE 3. OUTPUT FORMAT (HI1176) |      |                     |   |   |   |   |   |   |   |     |

|---------------------------------|------|---------------------|---|---|---|---|---|---|---|-----|

| ANALOG<br>INPUT                 |      | DIGITAL OUTPUT CODE |   |   |   |   |   |   |   |     |

| VOLTAGE                         | STEP | MSB                 |   |   |   |   |   |   |   | LSB |

| V <sub>RT</sub>                 | 0    | 1                   | 1 | 1 | 1 |   | 1 | 1 | 1 | 1   |

| •                               | •    |                     |   |   |   | • |   |   |   |     |

| •                               | •    |                     |   |   |   | • |   |   |   |     |

| •                               | •    |                     | _ | _ | _ | • | _ | _ | _ |     |

| •                               | 127  | 1                   | 0 | 0 | 0 |   | 0 | 0 | 0 | 0   |

|                                 |      |                     |   |   |   |   |   |   |   |     |

|                                 |      |                     |   |   |   |   |   |   |   |     |

### TABLE 3. OUTPUT FORMAT (HI1176) (Continued)

| ANALOG<br>INPUT |      | DIGITAL OUTPUT CODE |   |   |   |   |   |   |   |     |

|-----------------|------|---------------------|---|---|---|---|---|---|---|-----|

| VOLTAGE         | STEP | MSB                 |   |   |   |   |   |   |   | LSB |

| •               | 128  | 0                   | 1 | 1 | 1 |   | 1 | 1 | 1 | 1   |

| •               |      |                     |   |   |   |   |   |   |   |     |

| •               |      |                     |   |   |   |   |   |   |   |     |

| •               | •    |                     |   |   |   | ٠ |   |   |   |     |

| •               | •    |                     |   |   |   | • |   |   |   |     |

| Ţ               | Ū    |                     |   |   |   | • |   |   |   |     |

| V <sub>RB</sub> | 255  | 0                   | 0 | 0 | 0 |   | 0 | 0 | 0 | 0   |

# Adjustment Method

- V<sub>REF</sub> adjustment (VR1, VR2) The A/D converter reference voltage. V<sub>RB</sub> is adjusted by VR1 and V<sub>RT</sub> is adjusted by VR2. When self bias is used, there is no need for adjustment. Reference voltage is set to self bias mode at delivery.

- 2. Clamp reference mode voltage adjustment (VR3) Clamp reference voltage is set by VR3.

- DAC output full scale adjustment (VR4) Full scale voltage of the D/A converter output is adjusted to approximately 2.0V at shipment.

- Sync (clamp) pulse interface (VR5) This adjustment enables interface with the signal generator. At shipment, this adjustment is performed to obtain a threshold of approximately 2.5V to an H sync of 0V to 5V.

- 5.  $\overline{\text{OE}}$ , SEL, Sync, BLK,  $\overline{\text{CLE}}$ , Sync INT The following pins are set on the main board:  $\overline{\text{OE}}$ , SEL, Sync,  $\overline{\text{CLE}}$ , Sync INT (HI1176) and BLK (HI1171). For the pins function, refer to the specifications. The difference between Sync pin and Sync INT pin is that you input a pulse above 3.5Vp-p to Sync INT pin. The pulse threshold is set through VR5. For input through Sync pin, pulse is input at TTL or CMOS level. In this case cut the line between the Sync pin and Sync INT pin.

The PCB is shipped with the main board pins set as follows.

- OE Low (A/D Output ON)

- SEL Low (Pulse generated with Sync falling edge as trigger)

- Sync Line junction with Sync INT pin

- CLE Low (Clamp function ON)

- BLK Low (Blanking OFF)

- 6. Clamp pulse input method One method is to directly input the clamp pulse. Another method is to use the built-in multivibrator. The method used selected by using SW1. To use the built-in monostable multivibrator, it is necessary to mount the HI1176 sub board. R and C set the pulse width (ex. R = 130K, C = 100P,  $T_{PW} = 2.75\mu$ s).

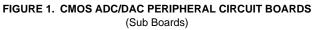

| ITEM                  | SYMBOL                | MIN | ТҮР | MAX | UNIT |

|-----------------------|-----------------------|-----|-----|-----|------|

| Clock High Time       | T <sub>PW1</sub>      | 25  | -   | -   | ns   |

| Clock Low Time        | T <sub>PW0</sub>      | 25  | -   | -   | ns   |

| Clock Delay           | T <sub>DC</sub>       | -   | -   | 24  | ns   |

| Data Delay A/D        | t <sub>PD (A/D)</sub> | -   | 18  | 30  | ns   |

| Data Delay<br>(Latch) | t <sub>DD</sub>       | -   | -   | 17  | ns   |

| Setup Time            | t <sub>S</sub>        | 10  | -   | -   | ns   |

| Hold Time             | t <sub>H</sub>        | 2   | -   | -   | ns   |

| Data Delay D/A        | t <sub>PD (D/A)</sub> | -   | 10  | -   | ns   |

## TABLE 4. TIMING CHART

# Notes on Operation

- 1. Reference voltage Shorting V<sub>RT</sub> and V<sub>RTS</sub>, V<sub>RB</sub> and V<sub>RBS</sub> will activate the self bias function that generates V<sub>RT</sub> = 2.6V and V<sub>RB</sub> = 0.5V. On the evaluation board either self-bias or the external reference voltage can be selected depending on SW2 and SW3. At shipment from the factory, reference voltage is in self bias mode. To provide external reference voltage, adjust the dynamic range (V<sub>RT</sub> V<sub>RB</sub>) to above 1.8V<sub>P-P</sub>.

- 2. Clock input There are two modes for the evaluation board's clock input.

- 1. provided from an external signal generator

- 2. using the crystal oscillator (built-in clock driver).

One of the two modes is selected using the switch SW4 on the evaluation board.

- 3. The 2 latch ICs, 74S174, are not absolutely necessary for the evaluation of the ADC and the DAC. Operation will still be normal if the ADCs output is directly input to the DAC. However, since the ADCs output is usually converted by a DAC after some signal processing, the 74S174s were mounted to provide a signal processing example.

- 4. Setting CLE High will disable the clamp function. The DC portion of the input signal will be blocked by C2. The ADC side of C2 will settle to about  $1/_2$  (V<sub>RT</sub> + V<sub>RB</sub>). If it is desired to DC couple the input to the ADC, remove R2 and short C2. Q3 can also be used as a buffer.

- 5. Clamp pulse latch On the evaluation board, the clamp is latched with the ADC sampling CLK and is then input to either the PW pin or Sync pin. A slight beat may be generated as vertical sag according to the relation between sampling frequency and clamp frequency. If there are no problems with  $V_{SAG}$ , latch is not necessary.

- 6. Prototype Areas There is a group of throughholes on the analog input, output, and logic. These can be used when mounting additonal circuits on the evaluation board. The connector hole on the DAC board is used to mount the test chassis and the mount jack.

4

Application Note 9329

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com